- 您现在的位置:买卖IC网 > Sheet目录329 > IDT71321LA20TFG (IDT, Integrated Device Technology Inc)IC SRAM 16KBIT 20NS 64STQFP

IDT71321SA/LA and IDT71421SA/LA

High Speed 2K x 8 Dual-Port Static RAM with Interrupts

Industrial and Commercial Temperature Ranges

Timing Waveform of Write with Port-to-Port Read and BUSY (2,3,4)

t WC

ADDR "A"

MATCH

t WP

R/ W "A"

t DW

t DH

DATA IN "A"

ADDR "B"

t APS (1)

VALID

MATCH

t BAA

t BDA

t BDD

BUSY "B"

t WDD

DATA OUT"B"

NOTES:

t DDD

VALID

2691 drw 10

1. To ensure that the earlier of the two ports wins. t APS is ignored for Slave (IDT71421).

2. CE L = CE R = V IL

3. OE = V IL for the reading port.

4. All timing is the same for the left and right ports. Port "A" may be either the left or right port. Port "B" is opposite from port "A".

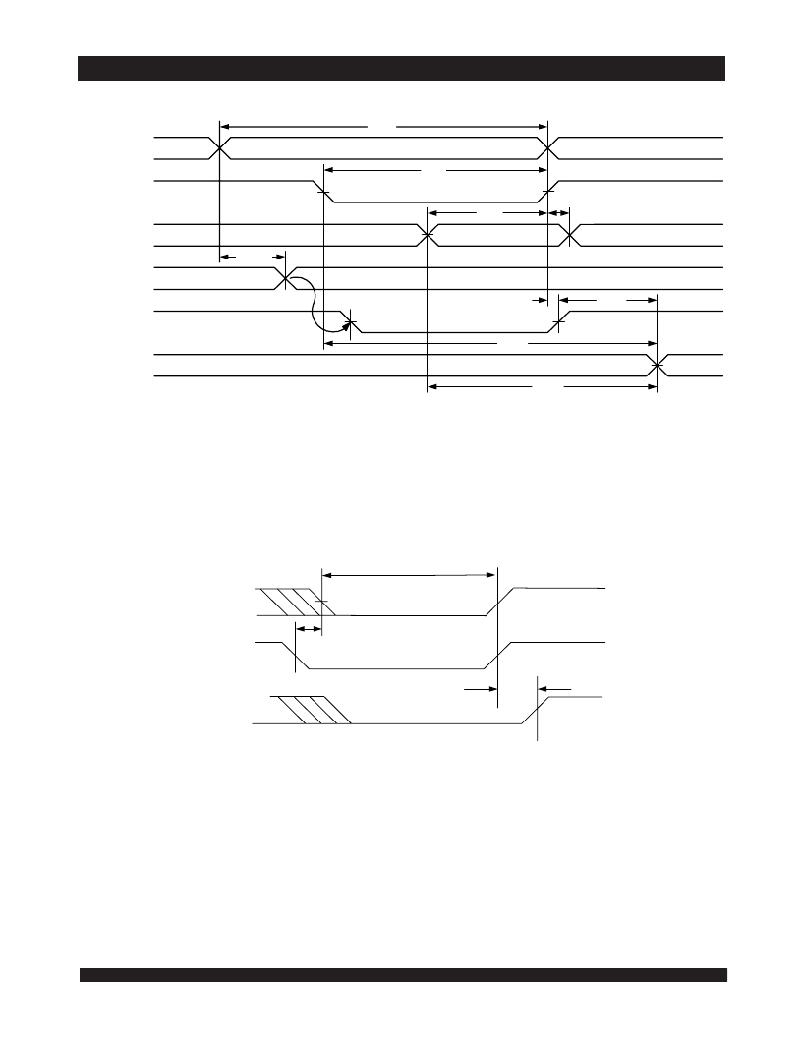

Timing Waveform of Write with BUSY (4)

t WP

R/ W "A"

t WB (3)

BUSY "B"

t WH (1)

NOTES:

R/ W "B"

(2)

2691 drw 11

,

1. t WH must be met for both BUSY input (IDT71421, slave) or output (IDT71321, Master).

2. BUSY is asserted on port "B" blocking R/ W "B" , until BUSY "B" goes HIGH.

3. t WB is only for the slave version (IDT71421).

4. All timing is the same for the left and right ports. Port "A" may be either the left or right port. Port "B" is opposite from port "A".

12

6.42

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

IDT71342LA25PFI

IC SRAM 32KBIT 25NS 64TQFP

IDT7134LA25JI

IC SRAM 32KBIT 25NS 52PLCC

IDT7140LA55C

IC SRAM 8KBIT 55NS 48DIP

IDT7142LA55C

IC SRAM 16KBIT 55NS 48DIP

IDT7143LA25G

IC SRAM 32KBIT 25NS 68PGA

IDT7164L25YGI

IC SRAM 64KBIT 25NS 28SOJ

IDT71T75802S200PFGI

IC SRAM 18MBIT 200MHZ 100TQFP

IDT71T75902S85BGG

IC SRAM 18MBIT 85NS 119BGA

相关代理商/技术参数

IDT71321LA20TFG8

功能描述:IC SRAM 16KBIT 20NS 64STQFP RoHS:是 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:72 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 同步 存储容量:9M(256K x 36) 速度:75ns 接口:并联 电源电压:3.135 V ~ 3.465 V 工作温度:-40°C ~ 85°C 封装/外壳:100-LQFP 供应商设备封装:100-TQFP(14x14) 包装:托盘 其它名称:71V67703S75PFGI

IDT71321LA25J

功能描述:IC SRAM 16KBIT 25NS 52PLCC RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:72 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 同步 存储容量:9M(256K x 36) 速度:75ns 接口:并联 电源电压:3.135 V ~ 3.465 V 工作温度:-40°C ~ 85°C 封装/外壳:100-LQFP 供应商设备封装:100-TQFP(14x14) 包装:托盘 其它名称:71V67703S75PFGI

IDT71321LA25J8

功能描述:IC SRAM 16KBIT 25NS 52PLCC RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:72 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 同步 存储容量:9M(256K x 36) 速度:75ns 接口:并联 电源电压:3.135 V ~ 3.465 V 工作温度:-40°C ~ 85°C 封装/外壳:100-LQFP 供应商设备封装:100-TQFP(14x14) 包装:托盘 其它名称:71V67703S75PFGI

IDT71321LA25JGI

功能描述:IC SRAM 16KBIT 25NS 52PLCC RoHS:是 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:72 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 同步 存储容量:9M(256K x 36) 速度:75ns 接口:并联 电源电压:3.135 V ~ 3.465 V 工作温度:-40°C ~ 85°C 封装/外壳:100-LQFP 供应商设备封装:100-TQFP(14x14) 包装:托盘 其它名称:71V67703S75PFGI

IDT71321LA25JGI8

功能描述:IC SRAM 16KBIT 25NS 52PLCC RoHS:是 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:72 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 同步 存储容量:9M(256K x 36) 速度:75ns 接口:并联 电源电压:3.135 V ~ 3.465 V 工作温度:-40°C ~ 85°C 封装/外壳:100-LQFP 供应商设备封装:100-TQFP(14x14) 包装:托盘 其它名称:71V67703S75PFGI

IDT71321LA25JI

功能描述:IC SRAM 16KBIT 25NS 52PLCC RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:72 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 同步 存储容量:9M(256K x 36) 速度:75ns 接口:并联 电源电压:3.135 V ~ 3.465 V 工作温度:-40°C ~ 85°C 封装/外壳:100-LQFP 供应商设备封装:100-TQFP(14x14) 包装:托盘 其它名称:71V67703S75PFGI

IDT71321LA25JI8

功能描述:IC SRAM 16KBIT 25NS 52PLCC RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:72 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 同步 存储容量:9M(256K x 36) 速度:75ns 接口:并联 电源电压:3.135 V ~ 3.465 V 工作温度:-40°C ~ 85°C 封装/外壳:100-LQFP 供应商设备封装:100-TQFP(14x14) 包装:托盘 其它名称:71V67703S75PFGI

IDT71321LA25PF

功能描述:IC SRAM 16KBIT 25NS 64TQFP RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:72 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 同步 存储容量:9M(256K x 36) 速度:75ns 接口:并联 电源电压:3.135 V ~ 3.465 V 工作温度:-40°C ~ 85°C 封装/外壳:100-LQFP 供应商设备封装:100-TQFP(14x14) 包装:托盘 其它名称:71V67703S75PFGI